视频地址:

http://player.bilibili.com/player.html?aid=31289365&bvid=BV1iW411d7hd&cid=89288170&page=12

课件地址:

该部分对应于书中的6.4-6.7。

- 当高速缓存大小大于数据的大小,如果分配良好,则只会出现冷不命中。

- 缓存不命中比内存访问次数影响更大

- 由内存系统的设计来决定块大小,是内存系统的固定参数。首先决定块大小,然后决定期望的缓存大小,然后再决定关联性,最终就能知道组的数目。

- 块的目的就是利用空间局部性

- 缓存是硬件自动执行的,没有提供指令集对其进行操作

- 建议:

- 将注意力集中在内循环中,因为大部分的计算和内存访问都集中在这里

- 按照数据对象存储在内存中的顺序,以步长为1来读数据,使得空间局部性最大。比如步长为2的命中率就比步长为1的命中率降低一半。

- 一旦从存储器读入一个数据对象时,就尽可能使用它,使得时间局部性最大。特别是局部变量,编译器会将其保存在寄存器中。

这一章主要介绍存储器层次结构中的高速缓存部分,包含在CPU中,使用SRAM存储器实现,完全由硬件管理。

1 高速缓存存储器

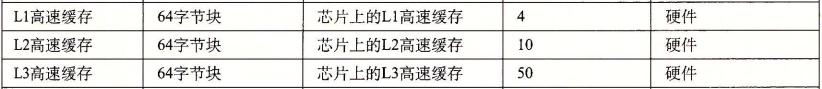

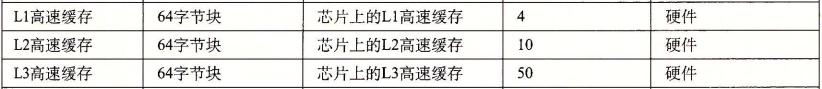

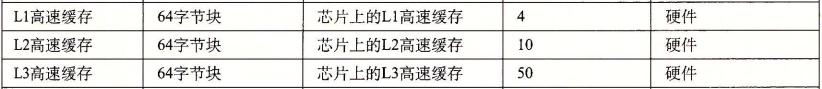

较早期的计算机系统的存储器层次结构只有三层:CPU寄存器、主存和磁盘,但是随着CPU的发展,使得主存和CPU之间的读取速度逐渐拉大,由此在CPU和主存之间插入一个小而快速的SRAM高速缓存存储器,称为L1高速缓存,随着后续的发展,又增加了L2高速缓存和L3高速缓存。

1.1 通用的高速缓存存储器组织结构