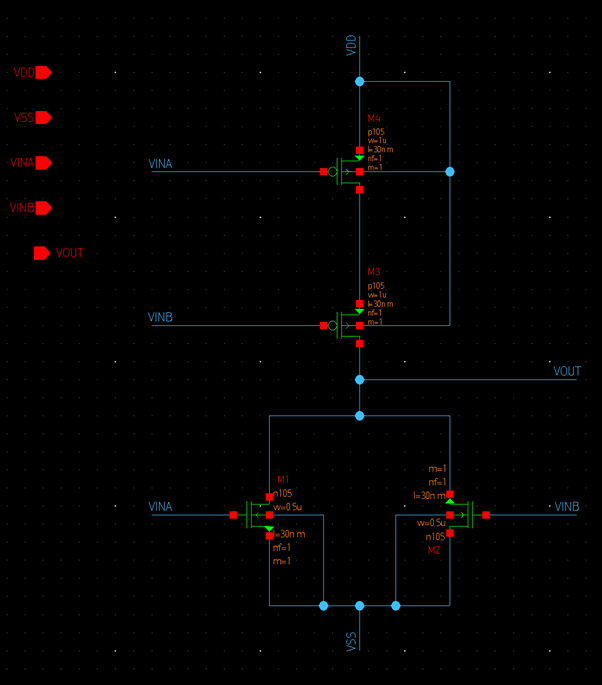

2-input NAND 게이트의 CMOS 트랜지스터 레벨 Schematic 설계입니다.

(와이어 연결, Pin.Label 설정은 이전 포스팅에서 다뤘으므로 넘어가겠습니다.)

PMOS 트랜지스터는 직렬로 연결되어 연결되어 입력이 모두 0일 때만 출력이 VDD에 연결되고, NMOS 트랜지스터는 병렬로 연결되어 입력 둘 중 하나라도 1이면 출력이 VDD에 연결됩니다.

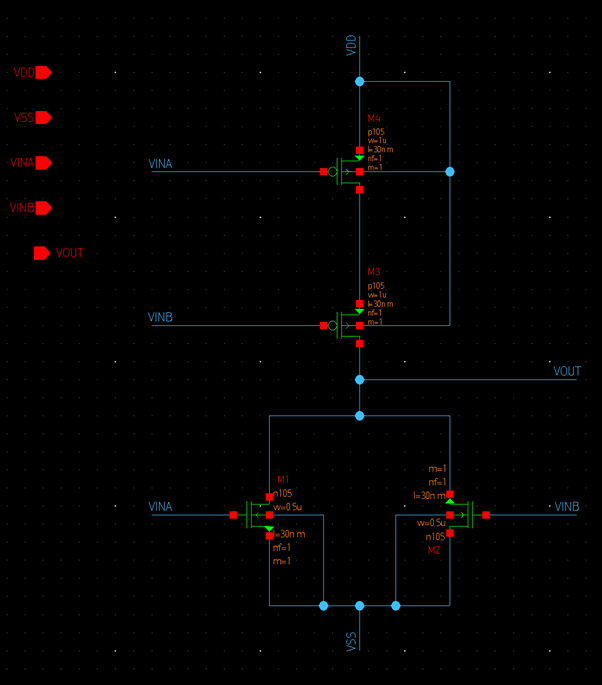

아래는 2-input NOR 게이트에 대한 Symbol View로, 입력(VINA, VINB)은 왼쪽에, 출력(VOUT)은 오른쪽에 배치되어 있습니다. 마찬가지로 VDD와 VSS는 위/아래에 배치되어 전원 연결이 용이하도록 구성되며, 출력 쪽에는 반전 기호인 ●이 포함되어 NAND의 논리적 특성을 표현해줍니다.

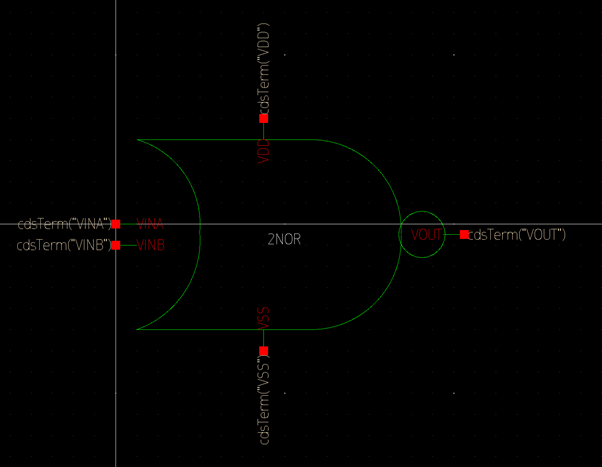

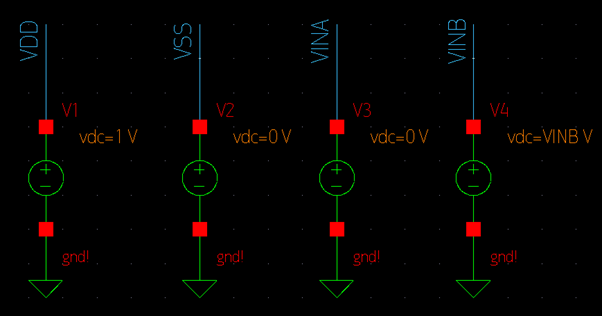

심볼 View로 생성한 2-input NOR 게이트를 상위 회로에서 인스턴스화하여 테스트벤치를 구성하였습니다.

시뮬레이션을 통해 2-input NOR 게이트의 특성을 분석하기 위해, 입력 A(VINA)을 0으로 고정하고, 입력 B(VINB)를 변화시키는 방식으로 구성했습니다.

NOR 논리 특성상,

즉, 출력은 B의 반전(~B)이 되어야 하며, 이를 통해 NOR 게이트가 올바르게 동작하는지 확인할 수 있습니다.

시뮬레이션을 위해 사용한 트랜지스터 모델을 정의한 라이브러리 파일(saed32nm.lib)을 등록합니다.

saed32nm.lib 파일에는 다양한 공정 조건에 맞춘 모델들이 정의되어 있으며, 이 중 FF(Fast-Fast) 코너는 트랜지스터가 빠르게 동작하는 최적의 조건을 가정합니다.