저번 포스팅에서 Sequential Logic에 대해 알아보고 Memory elements 중 하나인 Latch에 대해 알아봤습니다. 이번 포스팅에서는 Memory elements로 Latch가 아닌 Flip Flop이 필요한 이유에 대해 알아보고 다양한 Flip Flop을 구현해보겠습니다.

우리는 Clock의 rising 혹은 falling 엣지에서만 값을 update 해야 합니다. 하지만 Latch를 사용하면 Enable = 1 일때 계속 값이 update가 됩니다.

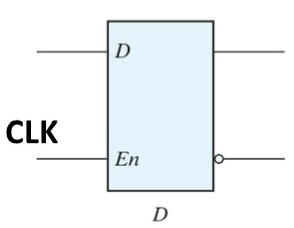

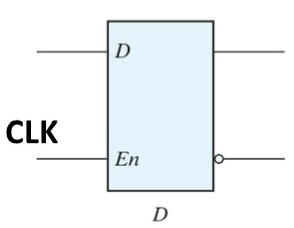

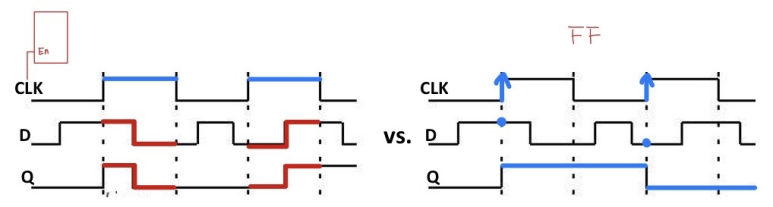

그렇다면 Latch에 Enable 신호에 Clock를 넣으면 되지 않을까요? 위 case와 Flip Flop을 비교해보겠습니다.

Latch의 Enable에 Clock을 연결하면 CLK = 1일때 D = Q 를 출력합니다. 그리고 CLK = 0 일때 이전 상태를 계속 유지하고 있습니다. 하지만 오른쪽 Flip Flop을 보면 CLK의 rising 엣지인 순간에만 D = Q 로 반영하고 다음 rising 엣지 이전까지 값을 유지하게 됩니다.

Latch는 CLK가 High 일때 계속 D = Q 로 반영되고 Flip Flop은 Clock의 rising 혹은 falling 엣지에서 D = Q로 반영됩니다.

그렇다면 왜 Latch는 Storage Element로 사용하지 못하고 Flip Flop은 사용할 수 있는 것일까요? 왜 Clock의 rising 혹은 falling 엣지에서만 값을 update 해야 하는지 지금부터 알아보겠습니다.

Latch를 Storge Element로 사용하지 않는 이유는 크게 **글리치(Glitch)**와 타이밍(Timing) 문제가 있습니다. Latch는 Clock가 안정적이지 않을 때 데이터가 의도치 않게 변할 수 있으며 이는 글리치(Glitch) 유발할 수 있습니다. 이러한 글리치(Glitch)의 발생은 데이터의 안전성에 영향을 미치며 타이밍이 민감한 회로에서 큰 문제가 될 수 있습니다.

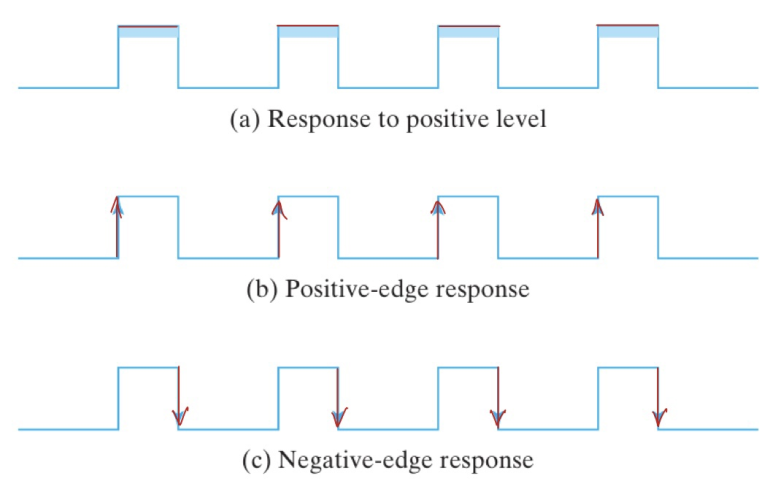

또한 Latch는 Clock의 Level(Low 혹은 High)에서 동작하기 때문에 데이터가 Clock의 Level이 유지되는 동안 언제든 전달될 수 있습니다. 이는 Clock이 Low 혹은 High인 상태에서 얼마나 오랜 시간을 머무는지에 따라 데이터 전달 타이밍이 달라질 수 있다는 것을 의미합니다. 이로 인해 타이밍 분석이 복잡해지고 원하는 타이밍 요구 사항을 만족시키기 어려울 수 있습니다.

이러한 이유로 우리는 디지털 회로 설계를 할때 Latch보다 Flip Flop를 선호하게 됩니다.

위와 같이 Latch는 Level 트리거이고 Flip Flop는 edge 트리거 입니다.